Wer die Debatte auf die Schlagzeile „Google umgeht MediaTek“ verkürzt, schaut am wahrscheinlich wichtigsten Punkt vorbei. Der Engpass bei den nächsten TPU-Generationen dürfte weniger im reinen Chipdesign liegen als in der Frage, wer bei TSMC rechtzeitig genügend fortschrittliche Fertigung und vor allem CoWoS-Packaging bekommt. CoWoS ist TSMCs fortschrittliche Packaging-Technik, die für viele KI-Beschleuniger zum Nadelöhr geworden ist.

Die vorliegenden Berichte stützen daher eher eine andere Lesart: Sollte Google seine Bestell- und Planungskanäle direkter zu TSMC ziehen, ginge es vor allem um Kapazität, Zeitplan, Kostenstruktur und Kontrolle. MediaTek wird in denselben Berichten weiterhin als wichtiger Partner für I/O-Design, Waferbeschaffung, Packaging-Integration und Qualitätskontrolle beschrieben[2][

10].

Zunächst: Ein komplettes MediaTek-Aus ist nicht bestätigt

Bislang stammen die Informationen aus Medien-, Analysten- und Lieferkettenberichten. Das taiwanische Wirtschaftsmagazin Business Weekly schrieb zu den Google-TPU-Projekten von MediaTek, MediaTek habe nicht kommentiert; TSMC erklärte demnach, keine Details zum Geschäft einzelner Kunden zu kommentieren[6].

Deshalb sollte die Aussage, Google werde künftige TPUs vollständig ohne MediaTek fertigen lassen, nicht als gesicherter Fakt gelesen werden. Belastbarer ist: Wenn Google Teile der Wafer- oder CoWoS-Koordination näher an TSMC heranführt, verändert sich vor allem die Kontrolle über Einkauf, Packaging und Zeitplan. Das bedeutet nicht automatisch, dass MediaTeks technische Rolle verschwindet.

Die gemeldete Arbeitsteilung: Google entwirft den Kern, MediaTek koordiniert wichtige Randbereiche

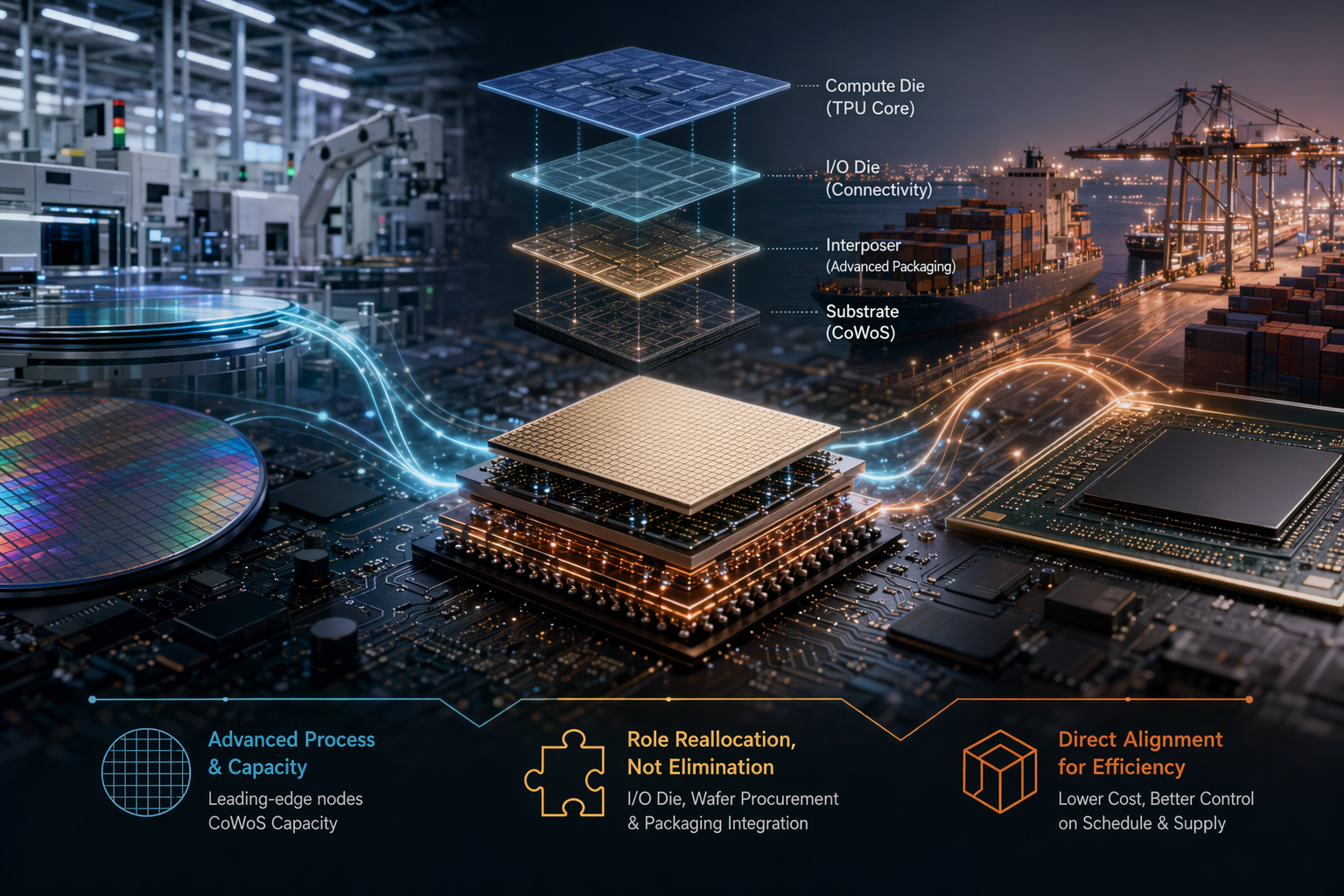

TPUs, also Tensor Processing Units, sind Googles speziell für KI-Berechnungen entwickelte Beschleuniger. In der aktuellen Berichterstattung wird die Zusammenarbeit mit MediaTek nicht als klassische Auslagerung des gesamten Chipdesigns beschrieben.

TechNews berichtet, Google übernehme beim gemeinsamen TPU-Projekt das Design des Compute Die, also des Rechenkerns, sowie die Beschaffung von HBM-Speicher. MediaTek sei dagegen für das I/O Die, die gesamte Waferbeschaffung und die Integration im Backend-Packaging zuständig[2].

Inside wiederum verweist auf The Information und schreibt, die nächste TPU werde weiterhin zum größten Teil von Google selbst entwickelt. MediaTek liefere vor allem Kommunikations-I/O zwischen TPU und verbundenen Komponenten, unterstütze bei der Qualitätskontrolle in der Produktion und fungiere als Besteller bei TSMC[10].

Das ist entscheidend: MediaTek ist in dieser Lesart weder bloß ein Durchreicher noch der alleinige Chefarchitekt der Google-TPU. Das Unternehmen sitzt vielmehr an Schnittstellen, Fertigungskoordination und Packaging-Integration. Genau diese Rollen können neu zugeschnitten werden, ohne dass jede technische Zusammenarbeit endet.

Warum TSMC so stark in den Mittelpunkt rückt

Bei modernen KI-ASICs entscheidet nicht nur, wer den besten Schaltplan entwirft. Ebenso wichtig ist, ob genügend fortschrittliche Fertigung und Packaging-Kapazität verfügbar ist. Hier kommt TSMC ins Spiel – und insbesondere CoWoS.

NextApple berichtete unter Verweis auf ausländische Medien, Google könne mit einer Doppel-Lieferantenstrategie über MediaTek und Broadcom zugleich um TSMC-CoWoS-Kapazitäten werben und so die Massenfertigung der TPU v7e beschleunigen[8]. Business Weekly berichtete zudem, MediaTek habe für Googles v7e- und v8e-Projekte zusätzliche fortschrittliche TSMC-Fertigung und CoWoS-Kapazitäten angefragt; die TSMC-CoWoS-Kapazität für MediaTeks Google-Projekt im Jahr 2027 solle demnach um mehr als das Siebenfache steigen[

6].

Auch der Zeitfaktor ist erheblich. Laut Business Weekly dauert es vom Fertigungsstart eines Wafers bis zum Abschluss von CoWoS-Packaging und Tests etwa acht bis neun Monate. Unter hohem Nachfragedruck könnten v7e-Vorserienausgaben, sofern die Zertifizierung reibungslos verläuft, sogar als lieferbare Massenprodukte behandelt werden[6].

Wenn der Flaschenhals so klar bei TSMCs Packaging- und Zeitplanressourcen liegt, ist es naheliegend, dass Google mehr direkte Sichtbarkeit und mehr direkten Einfluss auf diese Ressourcen haben möchte.

Vier plausible Motive für einen direkteren TSMC-Kanal

1. Google will knappe CoWoS-Kapazität absichern

Mehrere Berichte verknüpfen die Ausweitung von Googles TPU-Produktion direkt mit TSMCs CoWoS-Kapazität[6][

8]. Wenn die Nachfrage nach TPU v7e oder v8e schnell steigt, kann ein direkterer Zugriff auf Wafer- und Packaging-Zeitpläne die Planbarkeit erhöhen. Gerade bei KI-Infrastruktur zählen nicht nur Stückkosten, sondern auch die Frage, ob Rechenkapazität rechtzeitig verfügbar ist.

2. Kosten sind ein Motiv – aber kein bewiesener Automatismus

Inside berichtete unter Berufung auf The Information, Google plane mit MediaTek günstigere TPUs; ein Grund sei, dass MediaTeks Angebot unter dem von Broadcom liege[10]. Das zeigt: Google sucht offenbar nach einem kosteneffizienteren TPU-Modell.

Daraus folgt aber nicht automatisch, dass eine direkte Bestellung bei TSMC in jedem Fall günstiger wäre. Die tatsächlichen Kosten hängen von Verträgen, Kapazitätszusagen, Packaging-Konfigurationen und Risikoverteilung ab. Realistischer ist: Eine direktere Beziehung zu TSMC könnte bestimmte Abstimmungs- und Verhandlungsebenen reduzieren, garantiert aber nicht allein niedrigere Endkosten.

3. Eine kürzere Entscheidungskette kann die Produktion beschleunigen

In der gemeldeten Struktur übernimmt MediaTek nicht nur Designleistungen, sondern auch Waferbeschaffung und Backend-Packaging-Integration[2]. Laut Inside hilft MediaTek zudem bei der Produktionsqualität und bestellt bei TSMC[

10].

Wenn Google Fertigungsstart, Packaging, Tests und Zertifizierung enger steuern will, ist eine direktere Einbindung bei TSMC ein logischer Schritt. Das wäre dann eher eine Neuaufteilung der Zuständigkeiten: Wer kontrolliert Kapazität und Terminplan – und wer liefert I/O, SerDes, Qualitäts- oder Engineering-Unterstützung?

4. Google reduziert Abhängigkeiten von einzelnen ASIC-Partnern

Die Einbindung von MediaTek wurde bereits als Teil einer breiteren Risikostreuung interpretiert. NextApple berichtete, Google habe bei TPU-Architektur, IP, I/O-Diensten und Systemintegration früher stark auf Broadcom gesetzt; eine zweite Quelle solle Kosten-, Liefer- und Technologierisiken senken[8]. Inside schrieb ebenfalls, dass eine Zusammenarbeit mit Broadcom trotz MediaTek weiterbestehen könnte, wodurch Broadcom und MediaTek Googles TPU-Aufträge aufteilen würden[

10].

Ein direkterer TSMC-Kanal passt zu derselben Logik: Google bindet Designservice, I/O, Packaging-Integration und Kapazitätsverteilung weniger stark an einen einzigen Partner.

Was bedeutet das für MediaTek?

Für MediaTek wäre ein stärkerer Google-TSMC-Draht ein Risiko – aber nicht zwingend ein sofortiger Ausschluss. Die vorhandenen Berichte sprechen eher für eine mögliche Neuverteilung der Rollen.

TechNews schrieb, MediaTek sei in das Design von Googles achter TPU-Generation, TPUv8x, eingestiegen und erwarte ab dem vierten Quartal 2026 Umsatzbeiträge. Der Markt deute spätere Projektumsätze zudem als möglichen Hinweis auf TPUv8e[2]. Derselbe Bericht nennt MediaTeks langjährig entwickelte SerDes-IP als einen der Schlüssel dafür, Google-Aufträge von Broadcom zu gewinnen[

2]. SerDes steht für Serializer/Deserializer-Technik und ist für schnelle Datenübertragung zwischen Chipkomponenten zentral.

Daraus ergibt sich eine nüchterne Einordnung:

- Google könnte mehr Kontrolle über Wafer, Packaging und Liefertermine an sich ziehen.

- MediaTek könnte dennoch bei I/O Die, SerDes, Qualitätskontrolle oder Systemintegration beteiligt bleiben[

2][

10].

- TSMCs CoWoS-Zuteilung dürfte zum zentralen Hebel der Google-TPU-Lieferkette werden[

6][

8].

Deshalb können zwei Dinge gleichzeitig stimmen: Google kann den TSMC-Kanal direkter organisieren – und MediaTek kann weiter eine technische Rolle spielen.

Worauf man als Nächstes achten sollte

Erstens: Wer bekommt wie viel CoWoS-Kapazität? Die von Business Weekly berichtete mögliche Versiebenfachung der TSMC-CoWoS-Kapazität für MediaTeks Google-Projekt im Jahr 2027 wäre ein deutlicher Hinweis auf das Tempo der TPU-Ausweitung[6].

Zweitens: Wie läuft die v7e-Vorserie? Business Weekly berichtete, die von MediaTek für Google betreute v7e solle Ende des ersten Quartals 2026 in die Risikofertigung gehen; ob Vorserienausgaben direkt als lieferfähige Produkte gelten können, hänge vom Zertifizierungsverlauf ab[6].

Drittens: Verschiebt sich MediaTeks Rolle sprachlich und operativ? Entscheidend ist, ob MediaTek künftig weniger als Wafer- und Packaging-Koordinator und stärker als I/O-, SerDes-, Qualitäts- und Systempartner beschrieben wird. Genau dort verorten TechNews und Inside MediaTek derzeit – nicht als vollständig ausgeschiedenen Lieferanten[2][

10].

Fazit: Es geht um CoWoS und Kontrolle, nicht nur um einen Lieferantenwechsel

Falls Google bei nächsten TPUs direkter mit TSMC plant, wäre das vor allem eine Antwort auf knappe Kapazitäten, lange Produktionszyklen und den Wunsch nach mehr Kontrolle über die Lieferkette. Es wäre kein sicherer Beweis dafür, dass MediaTek technisch ersetzt wurde oder den Auftrag vollständig verliert.

Solange Google, TSMC und MediaTek keine klareren Angaben machen, ist die vorsichtigste Interpretation: Google macht seine TPU-Lieferkette direkter und breiter aufgestellt. Für MediaTek liegt das Risiko weniger in einem sofortigen Aus, sondern in einer möglichen Neuaufteilung der Kontrolle über Wafer, CoWoS-Packaging und Produktionszeitplan.